8位并行二进制全加器

的有关信息介绍如下:

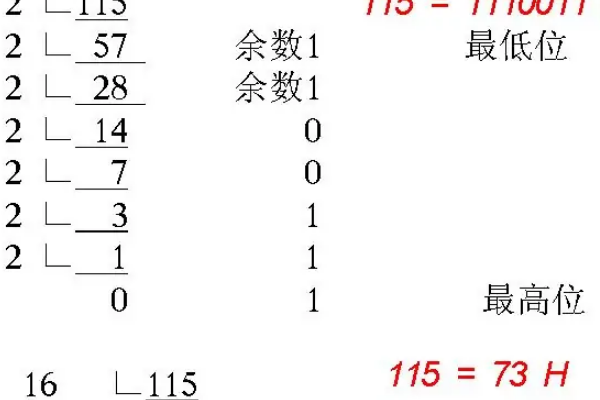

1、设计原理电路结构图或原理图电路功能描述定义了8位二进制全加器顶层设计元件端口信号,输入端口:AIN, BIN,是八个二进制数,数据类型被定义为STD_LOGIC_VECTOR。 CIN是输入的进位,数据类型IN STD_LOGIC;输出端口:SUM为和,数据类型IN STD_LOGIC COUT为输出的进位。 定义了7个信号C1, C2, C3,C4,C5,C6,C7作为器件内部的连接线,采用映射语句port map()将8个一位二进制全加器连接起来构成一个完整的全加器。低位全加器进位输出端连到高一位全加器的进位输入端,任何一位的加法运算必须等到低位加法完成时才能进行,这种进位方式称为串行进位2、实验程序程序1:半加器描述功 能:程序功能简介VHDL源程序代码LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;ENTITY H_ADDER IS PORT (A, B : IN STD_LOGIC; CO, SO : OUT STD_LOGIC );END ENTITY H_ADDER;ARCHITECTURE FH1 OF H_ADDER ISBEGIN SO <= NOT (A XOR (NOT B)); CO <= A AND B;END ARCHITECTURE FH1; 程序2:一位二进制全加器设计顶层描述功能:程序功能简介VHDL源程序代码LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;ENTITY F_ADDER IS PORT (AIN, BIN, CIN : IN STD_LOGIC; COUT, SUM : OUT STD_LOGIC );END ENTITY F_ADDER;ARCHITECTURE FD1 OF F_ADDER IS COMPONENT H_ADDER IS PORT (A, B : IN STD_LOGIC; CO, SO : OUT STD_LOGIC ); END COMPONENT; SIGNAL D, E, F : STD_LOGIC;BEGIN U1 : H_ADDER PORT MAP(A => AIN, B => BIN, CO => D, SO => E); U2 : H_ADDER PORT MAP(A => E, B => CIN, CO => F, SO => SUM); COUT <= D OR F;END ARCHITECTURE FD1; 程序3:8位并行二进制全加器顶层文件功能:程序功能简介VHDL源程序代码LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;ENTITY F_ADDER8 IS PORT ( AIN, BIN : IN STD_LOGIC_VECTOR(7 DOWNTO 0); CIN : IN STD_LOGIC; SUM : OUT STD_LOGIC_VECTOR(7 DOWNTO 0); COUT : OUT STD_LOGIC );END F_ADDER8;ARCHITECTURE ONE OF F_ADDER8 IS COMPONENT F_ADDER IS PORT (AIN, BIN, CIN : IN STD_LOGIC; COUT, SUM : OUT STD_LOGIC ); END COMPONENT; SIGNAL C1, C2, C3,C4,C5,C6,C7: STD_LOGIC;BEGIN U1 : F_ADDER PORT MAP(AIN => AIN(0), BIN => BIN(0), CIN => CIN, SUM => SUM(0), COUT => C1); U2 : F_ADDER PORT MAP(AIN => AIN(1), BIN => BIN(1), CIN => C1, SUM => SUM(1), COUT => C2); U3 : F_ADDER PORT MAP(AIN => AIN(2), BIN => BIN(2), CIN => C2, SUM => SUM(2), COUT => C3); U4 : F_ADDER PORT MAP(AIN => AIN(3), BIN => BIN(3), CIN => C3, SUM => SUM(3), COUT => C4); U5 : F_ADDER PORT MAP(AIN => AIN(4), BIN => BIN(4), CIN => C4, SUM => SUM(4), COUT => C5); U6 : F_ADDER PORT MAP(AIN => AIN(5), BIN => BIN(5), CIN => C5, SUM => SUM(5), COUT => C6); U7 : F_ADDER PORT MAP(AIN => AIN(6), BIN => BIN(6), CIN => C6, SUM => SUM(6), COUT => C7); U8 : F_ADDER PORT MAP(AIN => AIN(7), BIN => BIN(7), CIN => C7, SUM => SUM(7), COUT => COUT);END ONE;